Tim [Mithro] Ansell has a lot to tell you about the current state of open FPGA tooling: 115 slides in 25 minutes if you’re counting. His SymbiFlow project aims to be the GCC of FPGA toolchains: cross-platform, multi-platform, completely free, and all-encompassing. That means that it’s an umbrella framework for all of the work that everyone else is doing, from work on synthesis and verification tools, to placing and routing, to vendor-specific chip libraries. His talk catches you up with the state of the art at the end of 2019, and it’s embedded below. Spoiler alert: SymbiFlow has the big Xilinx 7-series FPGAs in its crosshairs, and is closing in. SymbiFlow is that close to getting a networked Linux system on the FPGA fabric in a Xilinx 7 today, completely independent of any vendor tools.

But let’s step back a sec for a little background. When you code for an FPGA, words you type get turned into a bitstream of ones and zeroes that flip perhaps a few million switches inside the chip. Going from a higher-level language to a bitstream is a lot like compiling normal programming languages, except with the twist that the resulting computational logic doesn’t map straight into a machine language, but rather into lower-level physical hardware on the FPGA. So “compilation” for FPGAs involves two steps: synthesis and place-and-routing. Synthesis takes the higher-level language that you write and turns it into a set of networks and timing requirements that represent the same logic, and can work across chip families. Yosys is the open-source synthesis tool of choice here.

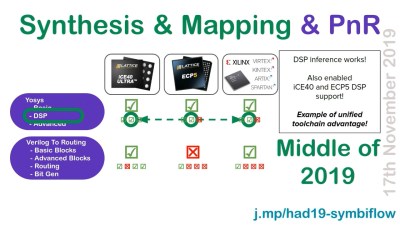

Place-and-route then maps the program logic into the individual FPGA’s architecture and feature set, and it’s here that reverse engineering work has and is being done to accommodate more FPGA families. nextpnr takes the program logic and maps it into FPGA gates, and it can’t do this without detailed descriptions of the various chips’ internals. For this, SymbiFlow splits each FPGA chip family into its own bitstream documentation and tooling projects. So far, we’ve got Project IceStorm for the Lattice iCE40 chips, Project Trellis for the Lattice ECP5s that were on the Supercon badge, and Project X-Ray for the Xilinx 7s.

Mithro starts the talk off by mentioning that the goal is to cover all FPGAs with one toolchain. That’s an incredible goal that’s far, far away. But progress is being made ridiculously fast. In early 2018, for instance, only the Lattice iCE40 parts were really well understood and supported. This FPGA was picked because it’s accessible, cheap, and was easy to reverse engineer, but Lattice’s market share is approximately zero. Xilinx and Altera are the Intel and AMD of the FPGA world, and without coverage of their chips, the project can only be said to be just getting off the ground. However, within a year, Dave Shah had essentially completely documented the much more powerful Lattice ECP5, and we were able to bring you the Hackaday Supercon Badge. So much for Lattice.

As alluded to in the opening, the real story here is the tremendous progress made in 2019 on Xilinx parts. As Project X-ray got seriously underway, some parts of nextpnr turned out to be more Lattice-specific than previously thought, and a new place-and-route tool Verilog to Routing developed at the University of Toronto, got pulled into SymbiFlow.

As alluded to in the opening, the real story here is the tremendous progress made in 2019 on Xilinx parts. As Project X-ray got seriously underway, some parts of nextpnr turned out to be more Lattice-specific than previously thought, and a new place-and-route tool Verilog to Routing developed at the University of Toronto, got pulled into SymbiFlow.

At the same time, some of the synthesis steps in Yosys weren’t taking optimal use of some of the more advanced functionality of the Xilinx parts, like the specialized digital-signal processing blocks (DSP), and made great progress on that front in 2019. (Of course, some of the optimizations of DSP on the Xilinx 7 chips spilled over to the Lattice ECP5s, so everyone wins.)

Which brings us to the punchline. Can SymbiFlow fully replace Xilinx’s proprietary (and unwieldy) Vivado toolchain? No, because the FPGA’s high-speed peripherals don’t play nice with the open place-and-route yet. And while Mithro said in the talk that the Symbiflow consortium were working full-out to get to that point by the end of 2019, we talked to him on Dec 29th, and they were still at it. But if you’re asking us, we’d predict that we will see a full and fully open Xilinx 7 toolchain in 2020. Maybe even this summer? It’s a project that’s near and dear to our hearts, so we’ll keep you in the loop.

But while Mithro, being a Linux/software guy at heart, is focused on getting a fully open toolchain to build up a Linux system, you shouldn’t be discouraged from trying anything else on the Xilinx 7 or Lattice parts right now. Both of these flows are entirely functional for microcontrollery or IoT applications. As long as you don’t need the high-speed memory and Ethernet peripherals, you’re good to go. And if you do need those things, you can synthesize with Yosys and do place-and-route with the closed Vivado tools until SymbiFlow ticks off a couple more boxes. There’s never been a better time than NOW to get started with FPGAs, IMHO.